- #Synplify pro component name how to

- #Synplify pro component name full

- #Synplify pro component name pro

- #Synplify pro component name code

Wa_cq_url: "/content/www/us/en/docs/programmable/683796/18-1/synopsys-synplify-support.

#Synplify pro component name code

5 The successful examples in Scicos-HDL 4-bit shift register Register is a logic component as a memorizer in computer and other digital system, the main element of it is trigger, every trigger can store one binary bit, so N bits binary code need the same number of triggers.

#Synplify pro component name pro

Wa_audience: "emtaudience:business/btssbusinesstechnologysolutionspecialist/developer/fpgaengineer", Synplify Pro 7.6, Quartus® II,Mux+plus II ,ISE, Modelsim, etc. Wa_primarycontenttagging: "primarycontenttagging:intelfpgas/intelquartussoftware/intelquartusprimedesignsoftware/intelquartusprimestandardedition", What you should do is keep the inline init to zero, but also add an external reset input that can also reset that register.Wa_emtcontenttype: "emtcontenttype:designanddevelopmentreference/developerguide/developeruserguide",

#Synplify pro component name how to

If you initialize that reg to 0, then synplify cannot make this optimization, but it warns you that the initializer is ignored because synplify does not understand how to actually initialize the registers as you can't do that on an ASIC. It notices that it can resolve that particular X to a 1, and as a result delete a bunch of logic. So, it seems that's what synplify is doing here. And then the tools can pick whatever value they like during synthesis if it can simplify the logic.

At any rate, all signals that are not explicitly initialized do not start at 0, they start at X (indeterminate logic level). And as a result, synplify handles initial blocks and inline initializers differently from FPGA tools - specifically, it mostly ignores them, even if it causes strange, unexpected behavior. For ASICs, it's common to not initialize anything, ever, and instead use explicit resets. Synplify is intended for synthesizing designs for ASICs, not FPGAs, and as a result is rather opinionated. The Go Board uses an external crystal for the clock.

#Synplify pro component name full

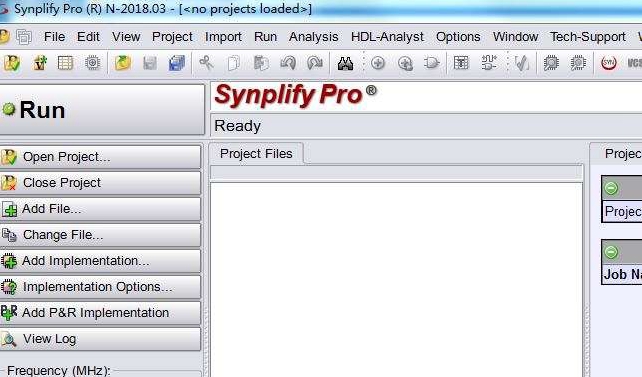

The full project is actually up on GitHub.ĮDIT 2: I also understand that a PLL Lock signal could be used as a power-on reset, but unfortunately the HX1K does not have any PLLs. And because Lattice can only initialize registers to 0, I want to use a power-on reset signal to set X/Y to non-zero values. I'd like the ball to start in the middle of the screen, not at (0, 0). The reason it does this is because ball_absolute has a pair of X/Y registers for the ball's position on the screen. The o_rst of this reset_generator component is hooked up to another component at a higher level like this: wire w_reset So why does the first version get optimized out? And why does adding an initial value that gets ignored change the behavior? Is this just a quirk of iCEcube2 and/or Synplify Pro?ĮDIT 1: I'm using a power-on reset because Lattice can only initialize registers to zero, and I'd like some to start off with non-zero values. This warning also implies that initial values are 0. Now it no longer is getting optimized out and works as expected, but iCEcube2 shows this warning: : reset_generator.v(13) | User-specified initial value defined for instance reset_gen.rst_count is being ignored. However, if I explicitly set rst_count to 0, like this: reg rst_count = 0 I thought all registers were initialized to 0, so I'm not sure why it thinks rst_count is always 1. Synplify then rebuilds the hierarchy to be as close as possible to the original source. ICEcube2 outputs this warning: : reset_generator.v(13) | Register bit rst_count is always : reset_generator.v(6) | Input i_clk is : ball_absolute_mv_vga_top.v(19) | Removing instance reset_gen (in view: work.ball_absolute_mv_vga_top(verilog)) of type view:work.reset_generator_4s(verilog) because it does not drive other instances.Īnd I can verify that the o_rst signal is indeed never set to 1. If I write the the module like this, it is getting optimized out: `default_nettype none I am synthesizing using Lattice iCEcube2 + Synplify Pro targeting an iCE40 HX1K on the Nandland Go Board.

We need to supply for'' atributes for our components in order for screen readers to correctly read out the component details for users with accessibility needs.

I am trying to write a Verilog module that generates a power-on reset signal for a few clock cycles. We're trying to address a bunch of accessibility issues, one in particular is proving quite difficult.

0 kommentar(er)

0 kommentar(er)